Dec 26th, 2010 - DS2x86 Alpha 0.01 release!

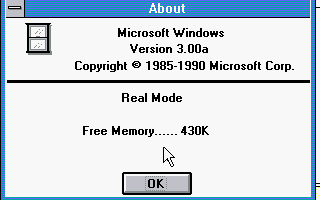

Well, here it finally is, the first alpha version of DS2x86! Please note that this is a very early alpha, and it has a lot of bugs and missing features. You should consider this just a test bench for my DSx86 port to the built-in 360MHz MIPS processor of the SuperCard DSTwo flash cart. But, since a few games seem to be somewhat playable already, and as I sort of promised an alpha version by the end of the year, here it is!

Installation

If you already have a working DSx86 installation on your flash cart, all you need to do is to copy the "DS2x86.plg", "DS2x86.bmp" and "DS2x86.ini" files into the "_dstwoplug" directory of your SD card. DS2x86 can use the same DSx86.ini file that you have used in the original DSx86. You can also use a separate DS2x86.ini if you wish to have different settings for DS2x86 and DSx86. NOTE! Do not confuse the two DS2x86.ini files! The one included in the zip file is the one required by the DSTwo plugin system, the one in the /data/dsx86 directory (and created by you) is the one used by the DS2x86 itself for game-specific configuration.

If you do not yet have the original DSx86 on your SD card, follow the instructions on my download page (or at DSx86 Compatibility Wiki). It is recommended you familiarize yourself with the original DSx86 first, before testing DS2x86. Or, you might want to wait for a more stable version of DS2x86 before installing it.

Limitations compared to DSx86

- Obviously, DS2x86 only runs on the SuperCard DSTwo flash cart, as it uses the MIPS processor of that cart, not the ARM processor of the Nintendo DS/DSL/DSi itself.

- Not all 80186 opcodes have been ported over yet, so some games that do run in the original DSx86 will not run in this alpha version yet.

- Audio support is very poor, only SoundBlaster 8-bit DMA audio is supported, all other audio output is still missing.

- ScreenMode "Jitter" was removed. If the configuration ini file uses Jitter, it will be replaced by Scale.

- ScreenMode "Scale" only works in MCGA and EGA modes, not in Text, CGA or Mode-X graphics modes.

- Screen refresh rate is locked to 15fps. I just recently noticed that there are various problems with both keyboard reading and screen refreshing when attempting to use higher refresh rates. I hope to fix these issues and allow faster screen refresh rates in the future.

- All high-resolution EGA, VGA and Mode-X graphics mode support is still missing. You will either get a black screen or the previous mode graphics sticking on the screen when going to high-resolution graphics mode.

- Mouse support is mostly missing, and what little support there is, is still completely untested.

- No blinking cursor on the DOS prompt.

Enhancements compared to DSx86

- Some 386-specific opcodes are supported. The support is blotchy at best, so it is more than likely you will run into an unsupported opcode when testing a 386-specific game.

- The x86 Parity and Auxiliary Carry flags are properly supported (it was architecturally impossible to support these properly in the original DSx86).

- The screen scaling uses proper linear interpolation, which produces better image quality than the hardware scaling used in the original DSx86.

- Speed! You can select the CPU speed between 60MHz and 396MHz, with the emulation speed ranging from 10MHz 80286 machine to 40MHz 80386 machine. Note that speeds lower than 240MHz might have stability issues, as the DSTwo interface can not keep up with the amount of data needing transfer.

Issues you might run into

- The keyboard reading has some synchronization issues when using non-default CPU speeds. If you notice key presses/releases to not get recognized, try changing the CPU speed (by clicking on the touchpad MHz indicator).

- If DS2x86 drops into the debugger, it has written a debug crash log into the dsx86dbg.log file. Please send this file to me so that I can add support to this opcode in future versions!

- You might also get a "Blue Screen Of Death" on the lower screen, stating that a certain exception has occurred. This does not get written to the log file (as the system status is unstable at that point), so if you can write the numbers down and email them to me, together with information about what you were doing, that would help me in improving DS2x86.

Thanks for your interest in DS2x86! Have fun testing it, and again, please remember this is a very early alpha version! Be surprised if something actually works, not if it fails! :-)

Dec 19th, 2010 - EGA & Mode-X work, Team Cyclops iEvolution

EGA & Mode-X work

During the past week I have mainly been working on adding pretty much all the EGA opcodes, and then adding most of the Mode-X specific opcodes. Both are currently so far along that many of the games supported in the original DSx86 seem to at least start up also in DS2x86. I also tested a couple of game trainer intros that I happened to have on my SD card. Those use 386 opcodes in real mode, and after I added the 386 opcodes that those needed, they are also starting up. These obviously do not work at all in the original DSx86, so DS2x86 will bring a little bit of extra compatibility already in the first alpha version! Here are screen copies of those, "brun_it!" by Eternity and "HexxTrnr" by Qwerty.

It would be interesting trying to get some proper 386-game running, but I still have so much stuff missing from the hardware support. Also the features that exist still have bugs (for example, Wolfenstein 3D does not read the keyboard properly, and Supaplex has problems in the palette animation), so that I think I need to focus on those before working on the 386 features. But, it is starting to look that even the first DS2x86 alpha version, to be released in a week or two, will be able to run a few games!

Team Cyclops iEvolution

Team Cyclops last week announced that their new iEvolution flash cart will allow the use of DSi mode for homebrew development. That means that when running on Nintendo DSi, a homebrew software has access to a faster CPU (133MHz instead of 66MHz, I believe) and more RAM (16MB instead of 4MB). They also offered a free iEvolution cart for "legitimate" homebrew coders. I contacted them, and they accepted me as one such, and will send me an iEvo flash cart. So, after I have got DS2x86 working properly, I could start working on a DSix86 version. :-)

I am not sure yet what needs to be done in a homebrew software to enable DSi mode with iEvolution, but I assume they have some kind of an SDK (or at least instructions on enabling it when using the normal devkitARM). With a two times faster processor and more RAM, I think it might be possible to add 386-opcode support into DSix86 as well. It would still not run all that fast, perhaps at a speed of a 20MHz 386 machine, but it would have some advantages over the DS2x86 version (namely the ability to use my existing ARM7 code with the AdLib emulation). I assume it would be much faster and easier to do the DSix86 port than it has been to do the DS2x86 port to a completely different CPU architecture. Some of the current DSx86 architecture (which I had to rethink for DS2x86) is not very well suited to adding support to 32-bit registers, so coding the DSix86 version will still take some time to do, but it should not take half a year! Anyways, I'll let you know when I receive the iEvolution cart and can see how it works.

Happy Xmas to everyone of you celebrating it!

Dec 12th, 2010 - DS2x86 EGA scaling

Last week I worked on the EGA opcodes. Currently the great majority of the opcodes (that are supported in DSx86) have been ported to DS2x86, so a couple of EGA games are already running fine. Some string opcodes are still missing, all the BIOS-based character output functions have yet to be coded, and I currently only have a blitting routine for the 320x200 resolution mode, so many games still fail. I just this morning decided to experiment with the EGA mode linear interpolation screen scaling routine. I first coded it by handling the palette calculations while blitting, and after I got that working I switched to a precalculated look-up-table that has the interpolated output pixel colors precalculated for each two input pixels. Since the 16-color EGA mode uses 4 bits per pixel, it is simple to lookup the output pixel value based on an 8-bit input value containing two adjacent pixels. The routine that handles the LUT filling whenever the palette value changes is obviously rather slow now, but since that specific routine is only used in the 16-color modes, and those rarely perform fast palette animations, this will most likely not be much of a problem. The actual blitting routine is almost as fast as the non-scaling routine, so there will be practically no performance penalty in using the scaled screen mode!

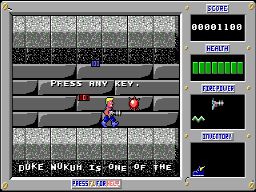

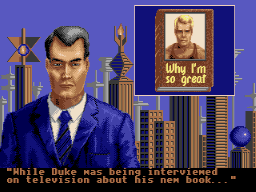

I was mainly interested in seeing what the scaling quality would be when scaling screens with some small text, so here below are screen copies of some screens from Duke Nukem 1 and Duke Nukem 2. In my opinion the text is for the most part quite readable, much better than with the hardware scaling as used in the original DSx86.

I also figured out a faster way to handle the separate memory access methods between normal RAM, EGA VRAM and ModeX VRAM. Since the graphics mode memory is organized so that each input byte addresse maps to a word address in the emulated VRAM, I now precalculate the two-bit-shifted memory addresses into the main page mapping table, so that the result address into the graphics memory can be taken simply by shifting the address generated by the common memory address calculation macro. Previously I first had to subtract the logical memory start address, then shift the value, and then add the physical graphics memory start address to the value. This simple change increased the Trekmo framerate by 0.5 fps, which together with some earlier general speedups now give a total framerate of 12.9 fps. Compared to the 11.9 fps value a few blog posts back, that is quite a nice increase. Now DS2x86 runs Trekmo at about the speed of a 40MHz 386 machine. There is most likely still room for improvement in various locations in the code, I just haven't yet figured out proper ways to improve them yet.

I have a two-week Xmas vacation starting on the 20th, so my current plan is to work on DS2x86 adding the most essential missing features, so that I can then release the first alpha version before the new year. Some of the biggest features that exist in DSx86 but are still missing from DS2x86 are:

- Mouse support.

- CGA graphics mode support.

- Other EGA modes besides the 320x200 resolution.

- Many Mode-X graphics opcodes are still missing.

- All graphics BIOS features besides setting the graphics mode are missing, the most essential being the BIOS character output features.

- All audio support (besides 8-bit SB digital audio) is still missing, and even that one still needs improvement.

- All the configuration features on the touchscreen (including updating the lower screen upper part based on the current configuration) are still missing.

- The blinking cursor in the text mode (command prompt) is missing.

- The crash logging feature is still missing.

- A lot of other minor things here and there.

Dec 5th, 2010 - DS2x86 EGA work

Last week was a very busy week at the office, we had a big customer delivery of our software, so that I did not even have time to work on DS2x86 on the evenings. Thus, nothing much has happened since the previous blog post. I started working on porting the EGA graphics code from the original DSx86 to DS2x86, though. That is a somewhat boring work, as it just means translating the same algorithms from ARM assembly to MIPS assembly. However, I decided to change the memory organization of the emulated EGA graphics to better suit the DS2x86 16-bit color screen blitting, so that will at least cause some changes.

Since the last blog post I have also improved the SB digital audio handling a bit, so that it now sounds pretty good in Wing Commander II. It is still not very good when playing LineWars II, most likely because LW2 uses very short DMA buffers and my 60Hz DMA buffer scanning rate in DS2x86 might be too slow for that. Other minor improvements include better debug screen handling, so that I can now print debug strings also while simultaneously showing the touchpad keyboard. This helps me in debugging the new features, but it won't affect the release version.

In general I have not had any problems with the DS2 SDK any more, DS2x86 seems now to start properly every time. Also my screen and audio updating routines seem to be quite robust at the moment, so that I can focus on improving the actual x86 emulation. There are still a lot of things missing, and my current focus is to get many of the same games that run in DSx86 running in DS2x86, so that I can release the first alpha version by the end of the year. After that I will focus on the 386-specific and protected mode features. The DS2x86.plg file is already almost 2 megabytes, and it takes 6 minutes to FTP-transfer to my DS Lite, which is quite annoying. I always try to think of something else to do while it transfers, but especially if there is a minor bug in the latest code, it is quite frustrating to fix the problem in a few seconds, build a new version, and then again wait over 6 minutes to see if the problem got fixed.

Tomorrow is the independence day of Finland, so it is a holiday and I can continue working on the EGA features. I hope to get something showing on the screen in an EGA game by tomorrow evening. That's all for this short blog post, hopefully I have something more interesting to tell in my next blog post. :-)

Nov 28th, 2010 - DS2x86 screen scaling revisited, audio work

Screen scaling revisited

After posting my previous blog post, I got an email from Gr�gori Mac�rio Harbs, who said that he is interested in screen scaling and interpolation algorithms, and has some ideas to share. He suggested a more efficient division of the pixel weights when interpolating over 5 input pixels to produce 4 output pixels. He had even gone so far as to provide an example of how the WC2 title screen would look with different interpolation methods, and he also provided some source examples. Many thanks for the tips Gr�gori!

Using the ideas that he provided, I was able to make the DS2x86 interpolation algorithm much faster, and also improve the quality. The new algorithm converts the first 4 input pixels with 75%/25%, 50%/50% and 25%/75% weighting to 3 output pixels, and the fifth input pixel is directly output as the fourth output pixel. Since the 25%, 50% and 75% values can be given as 1/4, 2/4 and 3/4, they are much simpler and faster to calculate than my original 80%, 60%, 40% and 20% weights.

Some other ideas that I learned from him for future use is the possibility to precalculate the weighted palette values beforehand, which would be especially useful when interpolating the 16-color modes, and the fact that bilinear interpolation of the Mode-X 320x240 screen is actually 5/4 interpolation on both axis. Neither of these I have implemented yet, but I am looking forward to when I have time to implement and experiment with these. Here below are the screen copies from my original interpolation algorithm (on the left) and the new improved algorithm (on the right). I think the new image looks noticeably sharper with fewer artifacts.

Audio work

By the end of last week I had gotten the new screen interpolation working, so I finally looked into DSTwo SDK audio support. I studied the example provided with the SDK, and then began to look into ways to implement that in DS2x86. Compared to the audio features of Nintendo DS itself, the audio support of the DSTwo SDK is very limited. It only supports one 16-bit stereo audio channel, which can run at 11025, 22050 or 44100 Hz. In DSx86 I had allocated one separate 8-bit audio channel to the SoundBlaster digital audio, one PSG audio channel to the PC speaker sounds, one 8-bit audio channel to the Covox or SB Direct DAC audio, and 9 separate 16-bit audio channels for the AdLib emulation. Packing all of these to the single stereo channel will be quite a challenge.

In DSx86 I coded the audio support so that it will be as close to the x86 method as possible. The game running in the main emulator will send the audio command bytes to an I/O port, which then get sent to the ARM7 side using the FIFO mechanism. The code running on ARM7 then interpreted these bytes (like it was the actual SoundBlaster card) and performed the proper operations. Now in DS2x86 I have to use the same CPU for both running the main emulation and handling the audio emulation.

I decided to start with the simple case of trying to get the SB digital audio channel working. I still used Wing Commander II as the test bench, as it plays speech during the game intro. In DSx86 I could run the separate audio channel at whatever frequency the x86 game requested, but now I needed to select one of the supported frequencies. I decided to go with the 22050 speed, as I thought that going to the full 44100 Hz will slow the emulation down unnecessarily. Since the input audio is 8-bit and I need to convert it on-the-fly to 16-bit and use interpolation to adjust the playing frequency, the quality will be pretty poor in any case, so 44100 Hz will certainly be overkill.

The SDK example had no timing features, it just used a spin loop to check when the audio buffer is free to handle the next block of the WAV file. It was not quite clear to me how the audio buffer interaction works, and whether handling the buffer filling in a timer interrupt (like in my screen handling) will work, so I spent quite some time experimenting with different methods of filling and swapping the buffers, with different buffer sizes. I need to have a timer interrupt running at 60Hz, so that I can use it to handle screen refresh and vertical retrace signalling to the x86 game (many of which sync to the screen retrace signal). I wanted to use this same interrupt for the audio buffer filling, mainly so that the screen contents sending and audio sending from the MIPS side to the ARM side do not conflict with each other. There are some difficulties syncing this 60Hz timer with the buffer filling, as there are three different buffer sizes that need to be taken into account. The ds2 audio buffer size needs to be divisible by 128, the number of samples played during each 60Hz period is 22050/60 = 367.5, and the third size is the DMA buffer length that the x86 game (in this case Wing Commander II) uses. In WC2 the buffer is 4000 bytes (not 4096 bytes), and the frequency it uses is 10752 Hz, so that each 4000-byte x86 DMA transfer will actually generate 8203 output samples.

The current status of my audio tests is that the SB digitized audio works in WC2, but the sound has some cracks and pops. I don't handle the continuing with the next DMA transfer after the previous has finished (and left a buffer only partially filled) properly yet, so I believe that is the cause for the cracks. However, the audio buffer filling happens inside a timer interrupt (which is not recommended in the SDK documentation), same as my screen update, and the game does not see anything wrong with the SB DMA IRQs and such, so I think I will get this working fine. I am currently using a 512-sample buffer (as the buffer obviously needs to have more than one 60Hz interval's worth of samples), but I will test whether different buffer sizes will improve things. Too long a buffer will cause a lag to the audio, so that is not helpful either.

In any case, still a lot to do on the audio front, but the big step forward was that I now understand the DSTwo SDK audio buffering method and can focus on working with it to implement the audio support in DS2x86.

Nov 21st, 2010 - DS2x86 screen scaling

Since last weekend I have been working on the I/O port handling and other things that already exist in DSx86 but which I had not ported over to DS2x86 yet. When I got DS2x86 running, I wanted to immediately start working on the protected mode stuff, so I left a lot of code commented out. Now I thought is a good time to port this code as well, so that DS2x86 could run most of the same games that DSx86 runs. I got most of the EGA/VGA port addresses done, and then also coded the MCGA graphics support, so that Wing Commander II will progress up to the part where it attempts to play digitized sounds.

After I had coded the straightforward MCGA mode blitting (where only a 256x192 window of the original 320x200 screen is converted to 16-bit color and copied to the DSTwo SDK internal buffers), I thought that this might be a good time to look into improved screen scaling methods. Many users of DSx86 have requested a smoother screen scaling method, but I have not yet added that as it needs going from the 256-color palette mode to 16-bit color mode. Now with DS2x86 I need to use the 16-bit color mode in any case, so this is a suitable test bench for the better scaling method.

The biggest problem with the more advanced screen scaling methods is that they are quite expensive computationally. The direct palette conversion code is reasonably straightforward, it just needs an extra table lookup to convert the palette index to a 16-bit color that can then be written to the output buffer, like this (shown for a single row):

la v0, BG_PALETTE // v0 = address of the palette table

1: lbu t3, 0(t1) // Get a byte (palette index) from VGA VRAM

addu t1, 1 // Increment input index

sll t3, 1 // Palette table has 16-bit values

addu t3, v0 // t3 = pointer to the palette table

lhu t3, 0(t3) // Get the 16-bit color from the palette table

addu t0, 2 // Increment output index

sh t3, -2(t0) // Store the 16-bit color to output table

bne t0, t2, 1b // Loop until one row done

However, even the simplest smooth scaling method, linear interpolation, needs a division and two multiplications per pixel. I am actually not sure how many CPU cycles multiplications and divisions take on the MIPS processor of DSTwo, but I assume they are more expensive than normal additions and subtractions. In any case, I used a calculator and some experimenting, and noticed that what I actually need is a way to smoothly draw 4 output pixels for every 5 input pixels (as 320/256 = 5/4). So, I have only four separate cases, and in fact the two rightmost output pixels are mirror images of the two leftmost pixels, so actually I only have two different cases. I was sure that I can come up with some shortcuts for these two situations, so I began to look into these more closely.

Linearly interpolating over 5 input pixels showed that the first output pixel should have a color of 80% of the first input pixel and 20% of the second input pixel. The second output pixel should have 60% of the second input pixel and 40% of the third input pixel. Mirroring these, the third output pixel should have 40% and 60%, and finally the last output pixel needs 20% and 80% weighting of the colors. To get rid of the divisions, I looked into multipliers that would let me divide the result by a power of two (so that I can use a shift instead of division). The first 80%/20% case is pretty close to 25/32 (78.125%) and 7/32 (21.875%), and the 60%/40% case is close to 5/8 (62.5%) and 3/8 (37.5%). I coded the first version of a linearly interpolating scaling code using simple shifts and additions to handle this pixel weighting, and I thought the result looked satisfactory, especially as the pixel weighting percentages are not quite correct. The code did not seem to cause any noticeable slowdown, even though it is still far from fully optimized. Here below are screen copies of the zoomed and scaled versions of the same Wing Commander II title screen.

Next I plan to start looking into the audio support. The whole audio playing technique in the DSTwo SDK is still completely unclear to me, as I haven't looked into it at all yet. That is the biggest feature still completely unsupported, so it is time to start working on it.

Nov 14th, 2010 - Trekmo running in DS2x86!

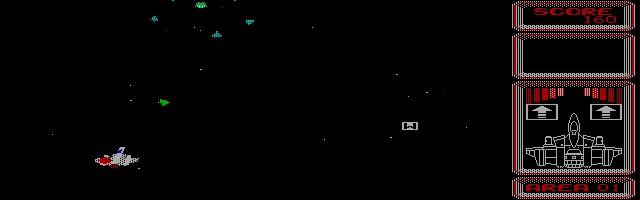

During the last week I kept adding opcode after opcode, with seemingly no change in how far Trekmo progressed in DS2x86. Trekmo uses a lot of trigonometric calculations and other algorithms before it actually draws anything on the screen, so it was rather boring adding all of these, and not even being sure whether I left some bugs in them or not. Then this Friday, after I had added yet another opcode, Trekmo suddenly began drawing the actual space scenes! So, here are some pictures of Trekmo running in DS2x86, to make up for the lack of screen copies in the last couple of blog posts. :-)

The interesting (and pleasently surprising) thing was that everything seemed to work properly! I had assumed that I must have coded at least some bugs in the arithmetic opcodes, so I expected to see broken polygons and possibly a complete crash after a few frames. There did not seem to be any problems, though. Trekmo progressed fine for several seconds, and then reached a yet another unsupported opcode. I thought this was enough for Friday, though, so I left adding the remaining opcodes later.

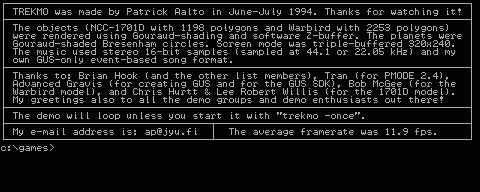

On Saturday morning I worked a while with an improved IRQ system (as the current system is far from optimized), but could not get it to work properly. I always have trouble with the IRQ system, it is by far the most difficult thing to get working in my emulator. In the end I had to roll back my changes, and decided to let the IRQ system be like it is for now, and work on getting Trekmo to run all the way thru to the end. Trekmo has a framerate calculator, so it can be used for benchmarking the combined CPU and graphics card system of a PC. In my Trekmo documentation I have a table of results from the systems I ran it on (back in 1994). The table has the following values:

| Machine | CPU | Graphics | Bus | Framerate |

|---|---|---|---|---|

| Compaq Prolinea 4/66 | 486DX2/66 | ET4000 | VLB | 40.7 fps |

| No-name clone | 486DX2/66 | Cirrus | VLB | 38.0 fps |

| Developed on this one: | 486/33 | ATI | ISA | 20.5 fps |

| AST Bravo LC 4/25s | 486SX/25 | Cirrus | VLB | 19.6 fps |

| Hyundai S386-C | 386/20 | S3 | ISA | 6.5 fps |

Finally today I managed to get Trekmo to run all the way to the end, so I was able to get a benchmark reading. Trekmo runs in DS2x86 (with the DSTwo MIPS processor running at 360MHz) at an average speed of 11.9 fps, which makes it noticeably slower than a 486SX/25 machine, but nearly twice as fast as a 386/20 machine. So, my original estimate of "a bit faster than a 386/33" machine is still valid. And, if I get the IRQ handling improved, it might still get a bit faster. However, I still have no audio support, and that in turn will make the emulation run slower, as I can not offload the audio handling to another CPU as I did in the original DSx86.

So, now that Trekmo is running, I need to find a new program to test. It would be interesting to try to get Windows 95 running, but I believe that is a bit too big a project to tackle at this point. DS2x86 still lacks a lot of protected mode opcodes, so perhaps I should instead try to make some 386-specific games (Zone 66, Doom) running. I should also start working on audio emulation, but it just feels so boring. I have already coded an AdLib emulation once, so coding it again for a different assembler does not feel like an interesting task.

Oh, by the way, GBATemp recently published my interview. Go ahead and read it in case you are interested in some background information about me and DSx86. Much thanks to Another World for interviewing me, it was a fun experience! I actually had to stop and think about some of the questions, as I hadn't really thought about some of the things mentioned in the interview before that.

Nov 7th, 2010 - Division trouble

After my last blog post I continued working on the new macro system, and kept adding new 386-opcodes using the new macros. This progressed nicely, until I ran into a div ecx opcode. The problem with the x86 division opcodes is that they use double-precision dividends. For example the opcode "div cx" divides a 32-bit value in DX:AX registers with a 16-bit divisor in CX register. Similarly, "div ecx" divides a 64-bit value in EDX:EAX with a 32-bit divisor in ECX. However, the MIPS architecture only has 32-bit divide operations, so I was able to code a 1:1 mapping between "div cx" and the MIPS equivalent, but I could not do this easily with the "div ecx" opcode of a 386 architecture.

I spent some time googling for solutions to this problem. The first potential solution was to use the GCC 64-bit (long long) division code. I tested it by coding a simple 64-bit division into my C-language tester program, and then looking at the dump file to see what exactly happens there. The GCC compiler uses a helper function __divdi3 to handle the actual 64-bit division, and the assembler code dump of that looked to be very big and complex. In addition to this divisoion result, the x86 div opcode calculates a remainder of the division. This has a similar __moddi3 helper function, which was just as complex. The register usage of my emulator differs quite a lot from the MIPS C-language standard, so if I called these functions I would need to save and restore many registers, which would slow the handling down even further. I decided to abandon this possibility and look for some more optimized versions of this 64bit/32bit division.

After some more googling I found an algorithm in a source code of some software by Jan Marthedal Rasmussen. The function is called double_div and it looked to be just what I was after. It calculates both the quotient and the remainder in one go, and it has special case handling for the simple situations, before reverting to the generic difficult scenario. I implemented this algorithm first in C language in my tester program, and compared the results it gives to the results of the GCC __divdi3 function. After I was certain the C language implementation works properly, I looked at the assembler dump and began converting that to a suitable format for my emulator. I could not directly use the assembler version that GCC had compiled, as it used much more registers than I can afford in my emulator code. I have four free registers that can be used in every opcode handler, and in rare occasions (luckily this "div" opcode is one of them) I can also use the four registers allocated for lazy flags handling. The C standard however leaves 16 registers free for every function to use, without having to save/restore them. The code that GCC created looked otherwise quite efficient, it had even managed to optimize away some repeated calculations of the original C code. Too bad I could not use it.

After some careful register allocation I managed to create a division opcode handler that looks to be working, however I have not yet created a proper unit test for it. I am currently more interested in continuing with the opcode macro system, so I'll go back to making sure this division opcode works even in the more difficult situations later. That is also why I won't post my algorithm here yet, I'll do that after I have created the unit tests and made sure my implementation works correctly.

But, now I think I'll continue with the opcode macros. I don't have any new screen copies to show either, as the code I am currently at is the code that calculates the ship and polygon positions before drawing them, so nothing new has yet been drawn on the screen. Perhaps next week. :-)

Oct 31st, 2010 - First graphics from Trekmo

DS2x86 has now progressed so far that I have managed to show the first title screens from my Trekmo demo! That is good progress, especially as I fought with a weird problem for the whole Sunday evening and Monday of the past week. Observant readers of my blog might have noticed something strange in the screen copy of my previous blog post. I myself only noticed the weirdness several hours after I had posted the blog post, when I was just proof reading the blog post again. The amount of EMS memory that 4DOS uses for swapping displayed 8197K! Normally it shows 224K, and there was no reason why it would suddenly start taking that much EMS (especially since I still only provide 1.5MB of EMS in DS2x86)! I looked at my latest changes in the code but did not see anything that would cause such a change, so I ran my opcode tester program, but that did not find anything wrong in any of the opcodes. I usually try to solve such weird issues before going to bed, as otherwise I just keep thinking about the problem and can not easily fall to sleep. This time it was already late Sunday evening so I had to leave the code like that.

On Monday after work I then began to really look into this problem. Luckily I had a working version in my backup directory, so I was able to run file compares between the source codes. The strange thing was that the real-mode opcode sources did not show any changes between the versions, while the problem was obviously in the real mode handling, as 4DOS stays in real mode all the time. After several hours of head scratching I finally figured out what the problem was. I had added a call to one of the real-mode opcode handlers from the protected-mode code, but had forgotten to make the required change into the real-mode handler that would allow it to be called from both real and protected mode. I had changed the main framework for this, though, which is why also the real-mode handling got broken. The file compare did not show this as the problem was that I had not changed the code where I should have, and the opcode tester did not find the problematic opcode because it was one of the simplest opcodes which I thought did not require a unit test! Argh! Well, several lessons learned again:

- If you use unit tests to test your code, make sure the unit tests test everything!

- No code is simple enough to not possibly get broken because of changes outside of the code.

- When you change existing code because of global framework changes, make sure you change every code affected by this, not just the code you are currently working on!

Anyways, after fixing that problem I managed to add the protected mode IRQ handling during the week. By Friday I had reached the location in Trekmo code that switches to graphics mode (Trekmo uses triple-buffered Mode-X 320x240 graphics mode). On Saturday morning I added the Mode-X blitting routine, which I ported directly from the DSx86 ARM ASM code into DS2x86 MIPS ASM, I just needed to add on-the-fly conversion from palettized 256-color graphics to 16-bit graphics (which is the only supported graphics mode in DSTwo SDK). Surprisingly, my new blitting code only had a single mistake. I had accidentally used sw (store word) where I meant sh (store halfword), which caused an unaligned crash, but after fixing that the blitting routine worked fine! I got the initial title pages (two simple PCX images) to display fine, and then I again kept running into various as of yet unsupported 32-bit opcodes and modrm variations.

Now I am working on the missing 32-bit opcodes. I finally figured out a way to use the GCC ASM macro syntax to embed register names into the branch target labels, so I am currently creating a new and improved macro system that would allow me to add several modrm bytes for several opcodes with just tiny additions to a single macro. This would speed up my opcode implementation quite a lot, and also remove one potential source of bugs caused by typos. I found out that if you add \() at the end of the parameter name, the parameter will work even within a word, so that a macro call like this :

#define eax s0

.macro modrm_3_help oper jump reg

\oper\()_\reg\()_SIB:

b \jump\()_\reg

.endm

modrm_3_help mov mov_r32_t0 eax

Generates code like this (as the symbolic register name s0 means register number 16):

mov_$16_SIB:

b mov_r32_t0_$16

So, I think I'll get back to improving the macro system now instead of making this blog post longer. :-)

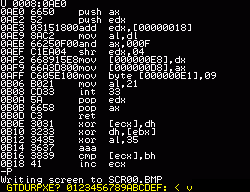

Oct 24th, 2010 - DS2x86 Protected Mode Interrupts

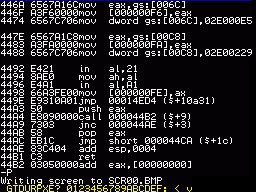

This past week was spent mostly just adding new 386-opcodes. Then by Friday evening I had reached a point in the Trekmo code where it tries to write a string to the screen. The easiest way to write to the screen in a DOS program is to call a DOS INT21 AH=09: WRITE STRING TO STANDARD OUTPUT routine. The DOS functions can not be called while in protected mode, so the PMODE header provides wrapper functions that first switch the CPU to real mode, then call the DOS function, and then switch back to protected mode. These functions are called via protected mode INT 33 (which curiously in real mode is a mouse interrupt), by giving the actual real mode interrupt number in AL register. The register values that the real mode interrupt needs as parameters are stored into memory variables for the protected mode INT 33 handler. Here below is the debug output of the "putdosmsg" routine in Trekmo.

|

putdosmsg PROC

push ax

push edx

add edx,_code32a

mov al,dl

and ax,0fh

shr edx,4

mov v86r_ds,dx

mov v86r_dx,ax

mov v86r_ah,9

mov al,21h

int 33h

pop edx

pop ax

ret

putdosmsg ENDP

|

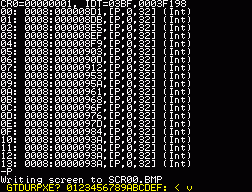

On Saturday morning I began working on the protected mode interrupt handling. The first step was to check the contents of the Interrupt Descriptor Table (IDT) that PMODE uses, to help me in understanding the behaviour of the code. Here below is the start of the IDT table. It shows for the first 19 interrupts the segment_selector:offset of the interrupt handler, the [Present, Descriptor Privilege Level, Gate Size] values of the descriptor, and finally in parenthesis the type of the gate. All of the IDT table entries in PMODE seem to be of the Interrupt Gate type, and they all point to a USE32 code segment.

I followed the algorithm that DOSBox uses in it's protected mode interrupt handling, but left out most of the tests for priority levels and different gate types. I need to refactor this code later, but for now I just want to get the code to work in this simplified situation in the PMODE header. After a while I managed to get the code to jump properly to the protected mode interrupt handler. The interrupt handler switched first down to 16-bit protected mode, and only then back to real mode. I did not have support in DS2x86 yet for either of these mode changes, so it took me a while to add that. By Saturday evening the code progressed all the way into the real mode DOS interrupt, and printed the string to the DS2x86 DOS text screen!

That was enough work for Saturday, so that was a good place to stop coding for a while. I was pretty happy to get that far with the protected mode interrupt handling (which I had feared to be a very complex issue) just in one day. Today I have been continuing with the code after the real mode interrupt handling, which is pretty much the reverse of the real mode interrupt call. After the real mode interrupt handler returns, PMODE header first switches to 16-bit protected mode, then sets up the GDT and IDT tables again, switches to 32-bit protected mode, and then finally returns to my Trekmo code from the INT 33 handler. I just an hour ago coded the "IRET" handling for the last step, and thus this is where I am currently at.

The next thing I need to do is to add protected mode IRQ handling. Trekmo waits for two seconds after displaying that string, before switching to graphics mode. This two second delay needs a working timer interrupt in protected mode, so I can not progress further in Trekmo until I have coded the IRQ handling. It should be relatively similar to the INT handling, though, so hopefully implementing it will not be very difficult.

I have no graphics mode support in DS2x86 yet, so I need to start working on that as soon as I get the IRQ handling done. I also soon need to start implementing the modrm bytes of the 386 opcodes properly. So far I have only implemented the few modrm bytes that I have encountered (just like I did when starting work on DSx86), so the code will not run anything besides Trekmo yet. I also need to enhance my tester program to test the 386-opcodes as well, to be sure that I have not coded a lot of bugs in them. But it is nice to see some progress all the time.

Oct 17th, 2010 - DS2x86 Protected Mode work

This past week has seen slow but steady progress with the protected mode support in DS2x86. After the previous blog post, I started thinking about ways to make the existing real-mode code more compatible with the needs of protected mode, and 32-bit memory access. In the original DSx86 code I had used all the 16-bit registers shifted to high 16 bits, and I used the lowest byte of the currently effective segment (which I kept in r2 register) to tell whether a segment override is in effect. Most of the opcodes need to know whether a segment override is in effect to calculate the correct memory address when using BP-based indexing. While memory access normally defaults to Data Segment (DS), addressing memory with the BP register defaults to Stack Segment (SS). In DSx86 I kept the currently effective segment register in r2 highest 16 bits, with the lowest byte telling whether a segment override is in effect. The SS register value was kept in the high 16 bits of r3 register, with the DS register value in the low 16 bits of the same register. Thus, in the main loop I could easily reset the segment override to be off and r2 register having the default DS register value like this:

ldrb r1,[r12],#1 @ Load opcode byte to r1, increment r12 by 1

mov r2, r3, lsl #16 @ r2 high halfword = logical DS segment, clear segment override flags

ldr pc,[sp, r1, lsl #2] @ Jump to the opcode handler

Can't get much more efficient than that, when trying to perform two

logically different operations, making r2 contain the currently effective

segment and clearing a segment override flag. The BP-based memory address

handling in turn checked whether a segment override is in effect and if

not, made the r2 register contain the current SS value with the following code:

.macro mem_handler_bp_destroy_SZflags

tst r2, #0xFF @ Is a segment override in effect? Zero flag will be set if not

biceq r2, r3, #0x0000FF00 @ r2 = logical SS segment in high halfword, with garbage in low byte

.endm

I had used a somewhat similar approach in DS2x86, as it was just copied

and translated to MIPS assembly from the DSx86 method. To prepare for

protected mode, I wanted to change this method so that the register that

keeps the currently effective segment (#defined to be "eff_seg", in reality

register ra) directly contains a linear memory address (which in

real mode would be the segment value shifted left 4 bits).

So, I could not use the same trick of storing the segment override flag

in this register. I really did not want to make the code slower than it

currently was, so I actually spent two days just thinking how I could

change the segment override flag handling so that the main loop would

not slow down (my first priority), I would not need to waste a new register

for just this flag (second priority), and that the BP register memory

access would also be as fast as possible (third priority).

After spending two days thinking about this problem, the solution finally occurred to me. In the end the main loop did not get any slower, I did not need to use a new register, and the BP addressing was just as fast as before! Here is the resulting code, with some explanation following.

lw t1, opcode_table(t1) // Get the opcode handler address from the opcode table

move eff_seg, eff_ds // Set DS to be the effective segment

ori flags, FLAG_SEG_OVERRIDE // Fix the CPU flags, telling we have no segment prefix

jr t1 // Jump to the opcode handler

After assembling, the generated code looks like this:

8006453c: 8d290000 lw t1,0(t1) 80064540: 01e0f821 move ra,t7 80064544: 01200008 jr t1 80064548: 37390002 ori t9,t9,0x2The MIPS assembler does a lot of changes to the original ASM code behind the scenes, due to the peculiar features of the processor. For example, all jumps and branches have a "branch delay slot" following them, which is actually executed before the branch is taken. The assembler reorders the opcodes so that the jump is moved before the preceding opcode, if the preceding opcode (ori in my example) has no effect on the branch instruction itself (which it does not here). If the jump can not be moved higher, then a NOP operation is added into the branch delay slot, wasting one CPU cycle. Also, as loads from memory (the lw opcode) cause a pipeline stall if the register that is loaded is used in the next opcode, you also lose a CPU cycle if you don't have any useful operations (that do not use the loaded register) to put immediately after the load opcode. Thus, there is no way to make the main loop code faster than what it currently is, so my first priority was fulfilled. I need to have one operation after the branch address loading, and I need to have an operation in the branch delay slot.

I managed to fulfill my second priority by using the x86 CPU flags emulation register (#defined as "flags", being in reality register t9). The x86 flags register has a reserved bit 1 (with value 2) that should always be set. I set this bit in the main loop, and then reset the bit to zero in all segment override handlers. Since the code that would need to use the full flags register value (practically only the PUSHF opcode handler) will never have a segment override, this will cause no problems in any code that handles the flags register.

The macro to handle the BP-register based segment handling looks like the following. The .set commands allow me to use the Assembler Temporary (AT) register myself, while normally the assembler uses this for all sorts of behind-the-scenes tricks and macro expansions.

.macro mem_handler_bp

.set noat

andi AT, flags, FLAG_SEG_OVERRIDE // at == 0 if we have a segment override

movn eff_seg, eff_ss, AT // If no segment override, put SS into effective segment

.set at

.endm

This is just as efficient as the original DSx86 code, just two

assembler opcodes. The andi opcode puts just the flags bit 1

into the AT register (so AT is zero if the flag is not on,

meaning a segment override is in effect), and the movn opcode

moves eff_ss register into eff_seg register if the AT register

is not zero (no segment override in effect). This fulfilled

my third priority.

In addition to this change I changed all my memory address routines to not use shifted memory offsets, which was a lot of work. There were 266 locations in the code where the shift was used, but only about 220 of these were related to this address calculation and needed changing. I first used a simple find-replace operation in the editor to comment all of these out, and then used my tester program to see which opcodes got broken, and then fixed these one by one. In the end the whole code got about 3% faster! Not a big change, but it was very nice that adding a new feature made the code faster, and not slower as normally happens!

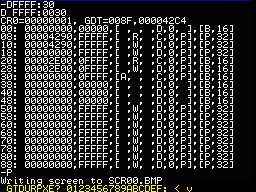

After such extensive code refactoring I finally got back to debugging the PMODE header of Trekmo in DS2x86. The PMODE header first goes to 16-bit protected mode (it jumps to a USE16 segment using the jmp 0020:138E opcode as you saw in the debug output of the previous blog post). Then it sets up the Interrupt Descriptor Table (IDT) while in the USE16 segment, and then goes to 32-bit protected mode (USE32 segment) using a RETF opcode. It took me the rest of last week to add support for the operations PMODE does in the USE16 segment, so that finally today I got DS2x86 to run the RETF opcode properly and switch to the USE32 segment. This is where I am currently at. There is only a small amount of code remaining in the PMODE header until it jumps to my own Trekmo code (jmp 00014ED4 in the debug output, which is the jmp _main command in the following code snippet from the PMODE sources).

I also hacked my debugger memory dump routines so that by dumping address FFFF:30 I can get a formatted output of the Global Descriptor Table (GDT). The GDT that PMODE uses is shown below. You can see that for example selector 20 is a USE16 code segment, while selector 08 is the actual USE32 segment (where the RETF opcode returned to, and where I am currently at). In this case PMODE uses a GDT with a limit of 0x8F (so that all the items happen to fit nicely into the DS2x86 debug screen) and located at linear address 0x000042C4.

p_start: ; common 32bit start

mov eax,gs:[1bh*4] ; neutralize crtl+break

mov oint1bvect,eax

db 65h,67h,0c7h,6 ; MOV DWORD PTR GS:[1bh*4],code16:nullint

dw 1bh*4,nullint,code16 ;

mov eax,gs:[32h*4] ; set up for new real mode INT32

mov oint32vect,eax

db 65h,67h,0c7h,6 ; MOV DWORD PTR GS:[32h*4],code16:int32

dw 32h*4,int32,code16 ;

in al,21h ; save old PIC masks

mov ah,al

in al,0a1h

mov oirqmask,ax

jmp _main ; go to main code

The next big thing to do is to add proper protected mode interrupt

handling using the IDT table, and I also need to improve my stack

handling so that switching between 16-bit SP and 32-bit ESP stack

pointer addressing works properly. Currently it is somewhat hardcoded

to just work in the current situation in PMODE/Trekmo. Besides those

features, I still have a lot of new opcodes to add, so these will again

keep me busy for quite a while.

Oct 10th, 2010 - Preparing for Protected Mode

This week my work on DS2x86 has been much less frustrating. The DS2x86 framework seems to be mostly working. I still get an occasional black screen when starting DS2x86, but that happens only once in every 20 starts or so. I decided to work on the actual emulation core for now and worry about the hangs later. Early this week I tried to decide on whether to continue porting the existing DSx86 features (like graphics and audio features), or to start working on proper 386 opcodes and protected mode support. I decided to go for the 386 and protected mode direction, as that is much more interesting and lets me study and learn new things.

I decided to start by trying to make my old Trekmo demo from 1994 run. Pretty much like I started with DSx86 by attempting to run my LineWars II game on it, I again use one of my old assembly language programs for testing. Having assembler source code available makes it much simpler to compare the debug output of DS2x86 with the original sources, to see where I am in the code and what is supposed to happen there. My Trekmo demo uses the PMODE DOS protected mode extender created by Thomas "Tran" Pytel. PMODE is small, simple and straightforward, but still supports various methods of entering protected mode (like DPMI, VCPI, and direct custom code). The good thing is that it also works without any memory managers present, so I can immediately concentrate on the low-level protected-mode support without having to worry about virtual memory and things like that. I still haven't coded proper support for the touchscreen keyboard to DS2x86, but that is not a problem as I can put the launch of Trekmo to the 4START.BTM file, so it starts running immediately when I launch DS2x86. It runs until it reaches a yet unsupported 386 opcode, and so I spent the last week iteratively adding new 386 opcodes and running DS2x86 again and again.

I also noticed that adding all the 386 opcodes means quite a lot of work. In addition to the new opcodes (that do not exist at all in a 80186 processor), all the existing opcodes have three new address or size variations. There are two new prefixes, 0x66 and 0x67, the first of which converts the size of the values handled from 16 to 32 bits, and the latter converts memory addresses similarly from 16 to 32 bits. So, with all the combinations there are 4 different cases for almost every existing opcode, and only one of them (with neither prefix) currently exists. The worst case result is that the executable size will more than quadruple after I have added all the new opcodes! A huge amount of work, so I am looking into other ways to handle these. I do need to code some of them using the current method, to get a feel for how they should work and what I can do to optimize the amount of work, though.

Anyways, as you can see from the screen capture above, by this morning I have just reached the location where PMODE.ASM enters protected mode. Entering protected mode means doing four things:

- Enabling the A20 address line. This is done by setting bit 1 (with value 2) of I/O port at 0x92, called System Control Port A. This is where I was at yesterday, and I had to do some changes to the memory address calculation routines to be able to directly address memory above the first megabyte in DS2x86.

- Setting up the Global Descriptor Table. This is done using the lgdt ASM command.

- Setting bit 0 (with value 1) of the CR0 Control Register. This actually puts the processor in protected mode.

- Performing a far jump using a CS segment selector (looked up from the GDT we set up before) to clear the prefetch input queue of the processor.

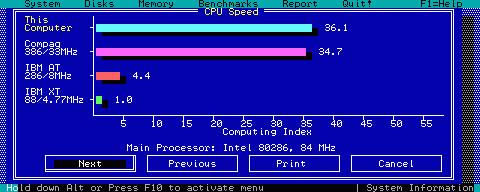

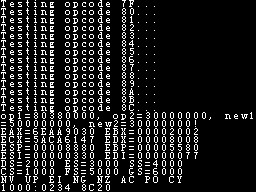

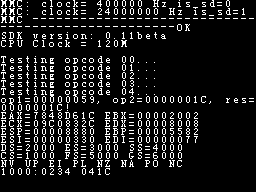

Oct 4th, 2010 - Proper DS2x86 speed test results

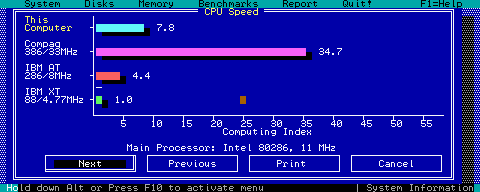

Just a quick update to the blog post of yesterday. After I had posted the message, I still tested the code further, and found out that the SDK timers do not run at the proper speed. This was again one cause for the weird hangs, and it also made all my speed test results invalid. The 60Hz timer ran actually at 264Hz speed, and the main PC timer which should run at 18.2Hz (and which is used by Norton Sysinfo for the speed tests) ran at almost 24Hz.

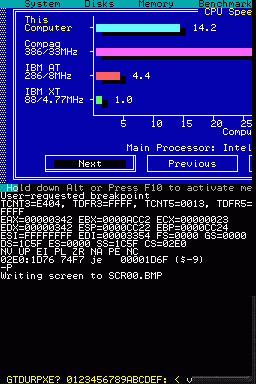

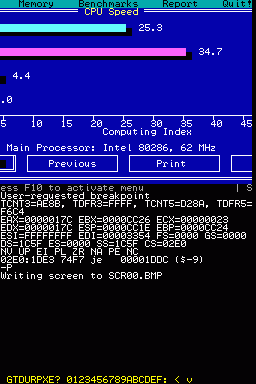

I just got the timers running at proper speeds, and ran the speed test again, using the fastest 396MHz MIPS CPU speed. Here is the result that I now believe to be correct.

The MIPS version of my x86 emulator runs at about 3.5 times faster than the ARM version, however the MIPS CPU runs at 6 times the clock speed. The difference is due to the Lazy Flags handling, the lack of various ARM tricks in the MIPS architecture, and the IRQ handling not using self-modifying code. I hope to be able to add some MIPS-specific tricks to the code while I get more familiar with the MIPS assembly, but even the current speed should make it possible and worthwhile to add 386-opcode support.

Oct 3rd, 2010 - DS2x86 frustration

The last week, and especially this weekend, has been very frustrating when working on DS2x86. It behaves very erratically, mostly hanging randomly, and when I try to add some debug output to pinpoint the problem location, it suddenly runs fine! Then I remove the debug strings, and it hangs again, but in a different location! Extremely frustrating. There is probably something seriously wrong in my IRQ handling, or perhaps I have misunderstood something about the underlying hardware.

Everything seems to work fine as long as I stay in the 4DOS command prompt. My first goal is to get Norton Sysinfo running, but that has proven to be much more difficult than I have anticipated. Yesterday I got it to run up to the main screen (where it shows the overview of the system), but even that happened only in about once every 5 tries, the other four tries it hanged before reaching that far.

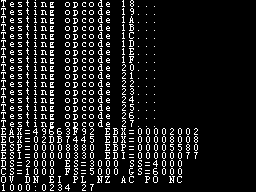

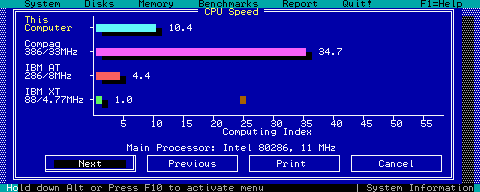

This morning I then removed some of the debug printing I had used to try to pinpoint the location, and then it suddenly reached the CPU speed test part without hanging! So, here is the first test result of the DS2x86 speed.

After that I tried to test with the fastest CPU speed of 396MHz, but could not get into the CPU speed test page without the system hanging. I then reverted back to the default 120MHz speed, but then everything started running in slow motion, and the one time that I got up to the CPU speed test page the speed showed something less than 4 times original PC!

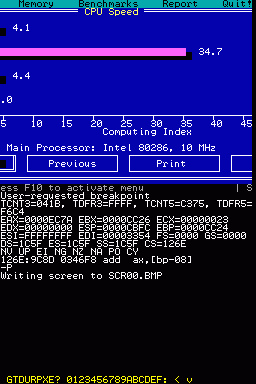

I made some more changes to the code but was not able to get back to the CPU speed test page. After a lot of tracing and debugging it finally began to look like the self-modifying code I use to handle IRQs might be the problem (or at least one reason for the hangs). I changed the code to use a normal variable to determine when to handle an IRQ, and finally got rid of the SysInfo hanging before the main screen. I made some more speed tests, the first one is with the CPU running at 396MHz and the second is with the 120MHz speed.

As you can see, there is not much sense in the results. The first result above with the 14.2 times original PC (when I had not specifically set the MIPS CPU speed), along with the results from 396MHz speed make sort of sense, but the result after setting the CPU speed to 120MHz is really weird. That would mean the DS2x86 would run at less than half the speed of the original DSx86. Anyways, I'll continue fighting with this and try to make some sense to the constant weird behaviour.

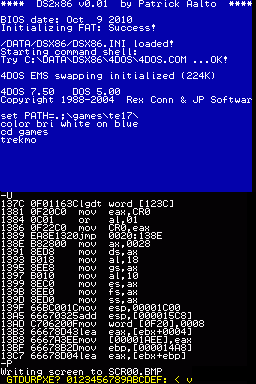

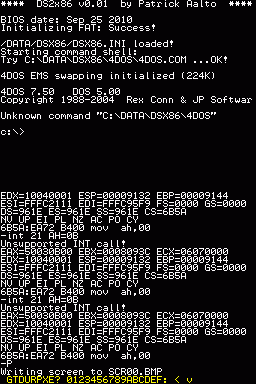

Sep 26th, 2010 - DS2x86 is starting up!

Okay, now I finally got some proper progress done with DS2x86! Yesterday I still fought with the screen update problem, and also had problems with the key input. Late yesterday I finally got the screen update to work without hanging, and also found the solution the the key input problem. I am using a couple of techniques that are unsupported by the current SDK, so I have had to come up with some hacks to work around the limitations of the SDK.

The first big issue was that the SDK only has one function to refresh the NDS screen, called ds2_flipScreen as it flips the two internal screen buffers. Using this function the current buffer gets sent to NDS and you can then start writing to the other buffer. I need to build the 16-bit 256x192 screen buffer from the emulated PC screen data, so I already have a sort of internal double-buffering. The screen contents that are being written to by the running software is separate to the buffer that gets sent to the NDS. I did not want to add another double-buffering layer and copy all the data for every single frame, but instead use only one buffer and (in text modes) only build the characters that have changed since the last frame.

Looking into the SDK dump files I found out that ds2_flipScreen calls a function called update_buf, that simply sends the current buffer to the NDS side, and luckily that function was not static so I could call it directly from my screen update code. However, it gets a handle variable up_screen_handle as it's parameter, and that is static to the SDK library, so I needed to add an ugly hack to find out the address of this variable from the original function, and then give this address as a parameter to the buffer update function. I added a call to this function to the timer interrupt handler, as the DSx86 architecture does not have a "main loop" that would refresh the screen contents once per frame. The underlying x86 code runs as fast as it can, and I just sample the screen contents using the timer interrupt several times a second.

I first tried to use this new method only for the upper screen and use the original SDK console functions for the lower screen, but that kept hanging the system constantly. I thought that perhaps the internal functions are not interrupt-safe, so that when the lower screen is in the process of updating the NDS side, and my timer interrupt happens in the middle of this and starts sending the upper screen data, this might be the cause for the hangs. So, I coded my own console functions for the lower debug screen and used the interrupt routine to update also the lower screen, and then finally I got the screen update system to work without hangs. This also had the advantage of increasing my debug screen from 32x24 characters to 42x24 characters. The bottom row commands got even harder to hit accurately with the stylus, though.

The next problem I had was that the SDK ds2_getrawInput function did not seem to report any key releases. Whenever a key was pressed, it stayed pressed until another key was pressed. This turned out to be caused by not calling the regist_escape_key SDK function to register a key to use for escaping to the console (or something, I am not quite clear about the use of the escape key). Why I need to register an escape key to get the keyboard input working properly is beyond me, and is probably a bug in the SDK, but in any case after calling that function I got the key input working for the debug screen. The default console in the SDK calls this function during InitConsole, so the key input works fine when using the default console.

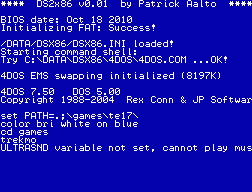

After that it was just a matter of porting the DOS functions so that I could try actually starting up 4DOS. This morning I then finally found and fixed the most serious problems in my ported DOS functions, and got 4DOS to progress up to the command prompt! I haven't yet checked where the "Unknown command" error message comes from, so there is probably still something wrong in my routines, but I was quite pleasantly surprised that my actual x86 CPU core emulation (which was completely written from scratch for the MIPS assembler) is already robust enough to run the 4DOS kernel!

This is about as far as I can get at the moment, as there are still a lot of stuff missing before I can even give any commands to the 4DOS prompt. I haven't coded any IRQ handling stuff yet (which is needed for the x86 code to read the keyboard I/O ports), all I/O port handling is still missing (so even when I get the IRQ handling done the IRQ has nothing to read yet), and all the bottom screen keyboard graphics are still missing (as the DSx86 keyboard graphics are 16-color and the DS2x86 graphics need to be 16-bit coloured). These should all be resonably straightforward, unless I run into some unforeseen obstacles when porting them from the current DSx86 code. But, in any case, I am pretty happy with the progress I have been able to achieve during the last week. Currently it looks like DS2x86 might actually be a reality one day. :-)

Sep 19th, 2010 - Slow DS2x86 progress

Last week was a very busy week at the office (first customer deployment of the software I have been working on), so I did not have much time (nor strength) to work on DS2x86 during the evenings. Yesterday I then worked on DS2x86 again, and in the end got it to compile and link. I had to comment out a lot of code, though, which I then need to write specifically for the DSTwo hardware environment.

I have run into various problems while trying to make the code build, so progress has been rather slow. Here is a list of various annoyances and other obstacles I have had to overcome.

- One big annoyance is the fact that every test build needs to be tested on the actual hardware. The DS2 SDK is quite a lot bigger than libNDS, and DS2x86.plg is already over 1.5 megabytes in size (while the current DSx86.nds file is around 0.7MB). Transferring a new build to my DS Lite using FTP takes almost 5 minutes, and it is really annoying to wait for the transfer to finish. I could keep swapping SD card between the DSTwo and the PC USB adapter, but I don't want to kill the mechanical contacts with too much use.

- Another annoyance is the unaligned access exception. There is an exception handler in the DS2 SDK, but it does not seem to do anything useful, the code just hangs whenever there is an unaligned memory access. These are easy to avoid in my ASM code (as it assumes everything is unaligned), but I have seen several cases where the compiled C code causes an unaligned memory access and hang.

- My Makefile skills are pretty rusty, and the Makefile that comes with the SDK is very basic. Thanks to an idea by another SDK user I was able to enhance the Makefile to be able to include binary data (as there is quite a lot of included binary data in DSx86), but this also resulted in unaligned memory access whenever the bin file size was not divisible by four. Looks like the mipsel-linux-as puts the 32-bit size value immediately after the actual binary data, with no regard to alignment! I had to pad all my binary files because of this.

- The default Makefile also does not handle dependencies properly. When a header file changes it does not compile all the C or C++ files that include that header file. I changed the makefile to use Advanced Auto-Dependency Generation and that finally seemed to fix the compilation problems. Before that I fought many times with weird compilation or linking problems, as I had not realized it did not compile everything it should have.

- While working on making the code build, I have also tried to study the hardware more closely. If the processor in the DSTwo is not exactly Ingenic Jz4732, it is something very similar to that. I found a nice overview about coding for the Dingoo A-320, which among other things has a header file with all the processor I/O address definitions. I have found out that the processor in DSTwo only seems to have 6 timers instead of 8. The timers that the SDK makes available are timers 4 and 5, and timer 0 is in use for some internal stuff. That leaves timers 1..3 free for software use. DSx86 needs several timers, so that was a useful find.

Anyways, I have now managed to output the boot strings (using the 6x8 pixel text font) onto the screen, but the screen update system in DSTwo SDK is still somewhat unclear to me. It uses double-buffering, but I don't need (nor want) to use double-buffering in text modes, so I am currently looking into ways to bypass the double-buffering scheme and be able to only update one buffer. The SDK does not include sources for the more hardware-specific stuff, so I have to look into the dump file to see what the internal routines do. All in all, quite slow progress, but at least I am getting forward.

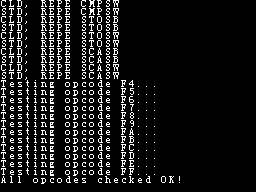

Sep 12th, 2010 - DS2x86 Opcodes Converted!

Just 5 minutes ago I got all the basic 80186 opcodes (including the REP-prefixed string opcodes) converted and tested! Hurrah! :-) Well, actually it is not much cause for celebration yet, as only now I can start coding the actual emulation framework around the CPU emulation. Many parts of the DSx86 framework are coded in C++, though, so porting those will be much faster than writing ASM code, which needs to be written pretty much from scratch for a new processor architecture.

Next, I think I will work on the interrupt architecture (as I need that to be able to input any keys and Norton Sysinfo needs a timer interrupt to be able to calculate the CPU speed). I am looking forward to getting Norton Sysinfo running, but before I can attempt that I need to add quite a bit of hardware-related stuff, including disk access support and the whole screen output stuff. Also, I need to start studying the DS2 SDK stuff more closely, so far I have only used the console output and not much else. I still have a lot to learn about it as well. But, it is interesting to learn new things!

Oh, and I also finally added a PayPal "Donate" button onto the Main Page, so you can donate a small amount to show your support of my working on DSx86. As I state on the main page, don't feel bad about not donating anything, I am not doing DSx86 for money. But at least you can now stop emailing me about wanting to donate money but not being able to. :-)

Sep 5th, 2010 - DS2x86 Work Continues

During the past week I have continued porting the DSx86 ARM ASM CPU emulation code to DS2x86 MIPS ASM. This work has progressed well, and I am actually a little bit ahead of schedule. I have now worked on it for 3 weeks, and I have about 80% of the 80186 opcodes coded. I have skipped and left for later some of the more difficult opcodes, like opcodes 0xCC..0xCE (INT3, INT imm8, INTO). The reason for skipping these has been the fact that they interface with the hardware features, and I can not test them properly with the current plain opcode tester program. These I need to revisit later, but I plan to first code all the normal opcodes and then switch over to the proper DS2x86 implementation and start adding the hardware features. If all goes well I might get all the normal 80186 opcodes done by the next weekend.

The problem above is where I am currently at, and this was again a problem in my tester code. The opcode is one of the shift opcodes, rol byte ptr [BX+SI],CL to be exact. The problem was that it assumed the CPU registers to be in the high halfwords of the actual hardware registers (like they were in DSx86). In DS2x86 I keep the register values like they are in a 386 processor, AL and AX are the low byte and word values of the EAX register, etc. This is one of the changes that I need to do to tester program for nearly every opcode it tests.

Aug 29th, 2010 - DS2x86 Progress, Lazy Flags implementation

DS2x86 Progress

Sorry, no new release of DSx86 today, as I have only been working on DS2x86 for the past two weeks. This porting work is progressing nicely, over half of the opcodes have been ported over to MIPS ASM. I have to mention, though, that the opcodes so far have been the easy ones (execpt the BCD opcodes), the more difficult opcodes like the string operations, shifts, INT and IRET, and port I/O are still ahead. These will take more time, and some of them will need some interfacing to the underlying hardware, so I can not just simply port them over from the ARM ASM code.

I am currently at opcode 0x8C, which is the mov r/m16,Sreg opcode, that is, moving a value from the segment register to memory or register. The problem above was caused by my tester code not yet supporting the FS and GS segment registers, while the CPU emulation already does this. So, every now and then I need to fix my tester program instead of the emulation code. :-)

Lazy Flags

Practically at the same time I started porting the opcode handlers from ARM ASM to MIPS ASM, I started thinking of ways to handle the Lazy Flags with the least amount of slowdown possible. Yesterday I figured out a method that is a little bit faster than the way I had when I started, so I spent a couple of hours refactoring all the opcodes I had already coded to use the new method. Too bad this did not occur to me earlier, but it is to be expected that I need to recode some parts of the code several times as I am still only learning the tricks in MIPS ASM.

I again used the DOSBox sources, together with the nice description at a www.emulators.com blog post, to figure out how the lazy flags need to work. There are six flags that change after each arithmetic operation in the x86 architecture, some of which are simple and some more difficult to determine after the operation. The flags are:

- Carry flag. This determines the unsigned overflow of the operation.

- Adjust Flag. This is similar to Carry, but for the low 4 bits of the operation.

- Overflow flag. This determines the signed overflow of the operation.

- Zero flag. This determines if the result was zero.

- Sign Flag. This determines if the result was negative.

- Parity flag. This determines the number of bits set in the low byte of the result.

The simple flags are Zero, Sign and Parity. Zero flag is set if the result was zero, Sign flag is set if the highest bit of the result was set, and Parity flag can be set by a 256-item lookup table based on the low byte of the result. These three flags behave similarly to all opcodes (that change flags), so they can be determined simply by the result of the last operation. The other three opcodes behave differently in different opcodes, so based on the calculation operations in the DOSBox sources I combined a list of the different cases, to see how these need to be handled. DOSBox names the result and operands lf_resd, lf_var1d and lf_var2d (for doubleword operands), and I named them lf_res, lf_val1 and lf_val2 in my code.

Carry

- Unknown, INC, DEC, MUL: return previous flag state

- ADD: return (unsigned)lf_res < (unsigned)lf_val1;

- ADC: return ((unsigned)lf_res < (unsigned)lf_val1) || (lflags.oldcf && (lf_res == lf_val1));

- SBB: return ((unsigned)lf_val1 < (unsigned)lf_res) || (lflags.oldcf && (lf_val2 == 0xffffffff));

- SUB, CMP: return ((unsigned)lf_val1 < (unsigned)lf_val2);

- SHL, SHR, SAR, ROL, ROR, RCL, RCR: All have different handling

- NEG: return lf_val1;

- OR, AND, XOR, TEST, DIV: return false;

Adjust

- Unknown: return previous flag state

- ADC, ADD, SBB, SUB, CMP: return ((lf_val1 ^ lf_val2) ^ lf_res) & 0x10;

- INC: return (lf_res & 0x0f) == 0;

- DEC: return (lf_res & 0x0f) == 0x0f;

- NEG: return lf_val1 & 0x0f;

- SHL, SHR, SAR: return lf_val2 & 0x1f;

- OR, AND, XOR, TEST, DIV, MUL: return false;

Overflow

- Unknown, MUL: return previous flag state

- ADD, ADC: return ((lf_val1 ^ lf_val2 ^ 0x80000000) & (lf_res ^ lf_val2)) & 0x80000000;

- SBB, SUB, CMP: return ((lf_val1 ^ lf_val2) & (lf_val1 ^ lf_res)) & 0x80000000;

- INC: return (lf_res == 0x80000000);

- DEC: return (lf_res == 0x7fffffff);

- NEG: return (lf_val1 == 0x80000000);

- SHL: return (lf_res ^ lf_val1) & 0x80000000;

- SHR: if ((lf_val2&0x1f)==1) return (lf_val1 > 0x80000000); else return false;

- OR, AND, XOR, TEST, SAR, DIV: return false;

Based on these lists, it seemed to me that the Carry flag will be the most difficult and time-consuming to calculate. Besides the obvious conditional jump opcodes, there are many other opcodes (ADC, SBB, RCL, RCR, CMC) that need the current Carry flag value as their input. Also the shift opcodes change and use the Carry flag in various ways, so it seemed to me that using a switch statement -style code to calculate the Carry flag lazily whenever it is needed will really slow down those operations. So, I decided to see how much extra code I would need if I went for a direct Carry flag calculation in each of the opcodes. It turned out that most of the times it only takes one ASM operation to calculate the Carry flag after the operation, so this is how I currently handle the Carry flag.

I also noticed that if I calculate the Carry flag separately, I can fake the lf_val1 and lf_val2 values in opcodes like INC and DEC to give me the correct Adjust flag value when using the same calculation code as the normal ADD/SUB opcodes use. So I was able to simplify the Adjust flag calculation to the one case: ((lf_val1 ^ lf_val2) ^ lf_res) & 0x10. This just left the Overflow flag which needs separate cases for each opcode type. I use one of the MIPS general purpose registers to keep track of the last opcode type, along with registers for the last result and operands, so that the Overflow flag can be calculated lazily whenever needed. I hope to figure out some speedups for this as well, but for now it will have to do.

To show an example of the actual opcode handling and what the Lazy Flag handling requires, here is the handler for ADC r/m8,r8 opcode when the left operand is a memory address. In DS2x86 I decided to have #defines for all the registers I use for emulation, so I don't need to remember which MIPS register was which. I did not do this in DSx86, and that caused some wrong register usage from time to time.

.macro adc_effseg_reg8l reg get_CF_into t3 // t3 = Carry flag value li lf_type, OF_CALC_ADD | 24 // Remember the operation type and shift value for Lazy Flags lbu lf_val1, 0(eff_seg) // Load the left operand from RAM andi lf_val2, \reg, 0xFF // Remember the right operand for Lazy Flags addu t3, lf_val1 // t3 = lf_val1 + Carry addu lf_res, t3, lf_val2 // lf_res = lf_val1 + Carry + lf_val2 srl t0, lf_res, 8 // t0 = Carry value sb lf_res, 0(eff_seg) // Save the result to RAM andi lf_res, 0xFF // Remember only the low 8 bits for Lazy Flags j set_carry_from_t0 // Back to loop .endmThe get_CF_into macro looks like the following. It is a macro so that I can later change how the Carry flag is calculated without having to change all the code that uses it (just in case I still need to revert back to lazy calculation of the Carry flag). The set_carry_from_t0 code is immediately before the opcode loop handler, as many opcodes jump there to store the t0 register value back into the flags register lowest bit. When calculating the Carry flag immediately, Carry is simply the 8th bit of the result, so I can just shift it to the lowest bit of t0 register and don't need to handle the complex ((unsigned)lf_res < (unsigned)lf_val1) || (lflags.oldcf && (lf_res == lf_val1)) algorithm at all!

.macro get_CF_into reg andi \reg, flags, 1 .endm

As you can see from this code, even just remembering the result and operands for later calculation of Lazy Flags takes a lot of code, in this case 4 of the 10 ASM operations are there just to get the later flags calculation to give correct result. When coding for the ARM ASM I did not need any of these, as the ARM can keep track of the flags by itself. Thus, DS2x86 will not be as much faster than DSx86 as the difference in the CPU clock speeds would make you think.

Aug 22nd, 2010 - DS2x86 Progress

I got my free DSTwo flash cart last Monday, so I have been working on DS2x86 ever since. It took me all of Monday evening to get the DS2x86 framework (tester routine calling the MIPS ASM CPU emulation code, and it returning properly back to the tester routine) to run without crashing, so on Tuesday evening I was able to start working on the actual CPU opcode emulation with MIPS ASM language. I am actually using a strict TDD (Test Driven Development) coding technique when working on DS2x86. With DSx86 I usually coded something, then tested it with some test games, and only if that failed I coded more thorough tests. With DS2x86 I implement the test routines (or improve the old tests I used in DSx86) first, and only then start coding the actual opcode handlers. I do this because the MIPS ASM language is very unfamiliar to me, and also because I am now using the Lazy Flags approach, so I can no longer use the ARM CPU to calculate the correct x86 CPU flags for me.